ケイデンス、新たなチップレットエコシステムで市場投入を加速

ケイデンスの新たなチップレットエコシステムの発表

2023年1月6日、米国カリフォルニア州サンノゼに本社を置くケイデンスが、最新のチップレットエコシステム「Chiplet Spec-to-Packaged Partsエコシステム」を発表しました。このエコシステムは、フィジカルAI、データセンター、高性能コンピューティング(HPC)向けのチップレット開発において、設計の複雑さを軽減し、市場投入までの時間を短縮することを目的としています。

初期IP提供パートナーには、Arm社やArteris社、eMemory社などが名を連ねており、半導体解析技術パートナーとしてはproteanTecs社も参加しています。これにより、チップレットの導入を円滑に進めることが期待されています。さらに、ケイデンスはSamsung Foundryと協業し、同社のSF5Aプロセス上でのパートナー提供のIPを事前に統合し、手元での半導体試作品デモを行うことが計画されています。

協業の重要性と影響

ケイデンスとArm社は、長年にわたる協業関係をさらに深化させ、フィジカルAI及びインフラAIの分野におけるイノベーションを加速する取り組みを強化しています。今後はArm® Zena™ Compute Subsystemを活用することで、フィジカルAIチップレットプラットフォーム及びChiplet Frameworkを強化する見通しです。これにより、自動車、ロボティクス、ドローンなどの次世代エッジAI向けの処理要件や、データセンターで求められる標準I/O及びメモリチップレットのニーズに対応します。

「設計の複雑さを軽減することで、低リスクでの先進的なチップレット導入が可能になります。」とケイデンスのDavid Glasco(Vice President of the Compute Solutions Group)はコメントしています。このエコシステムは、よりスマートで安全かつ効率的なシステムの実現に寄与することを目指しています。

EDAフローの効率化と相互運用性を追求

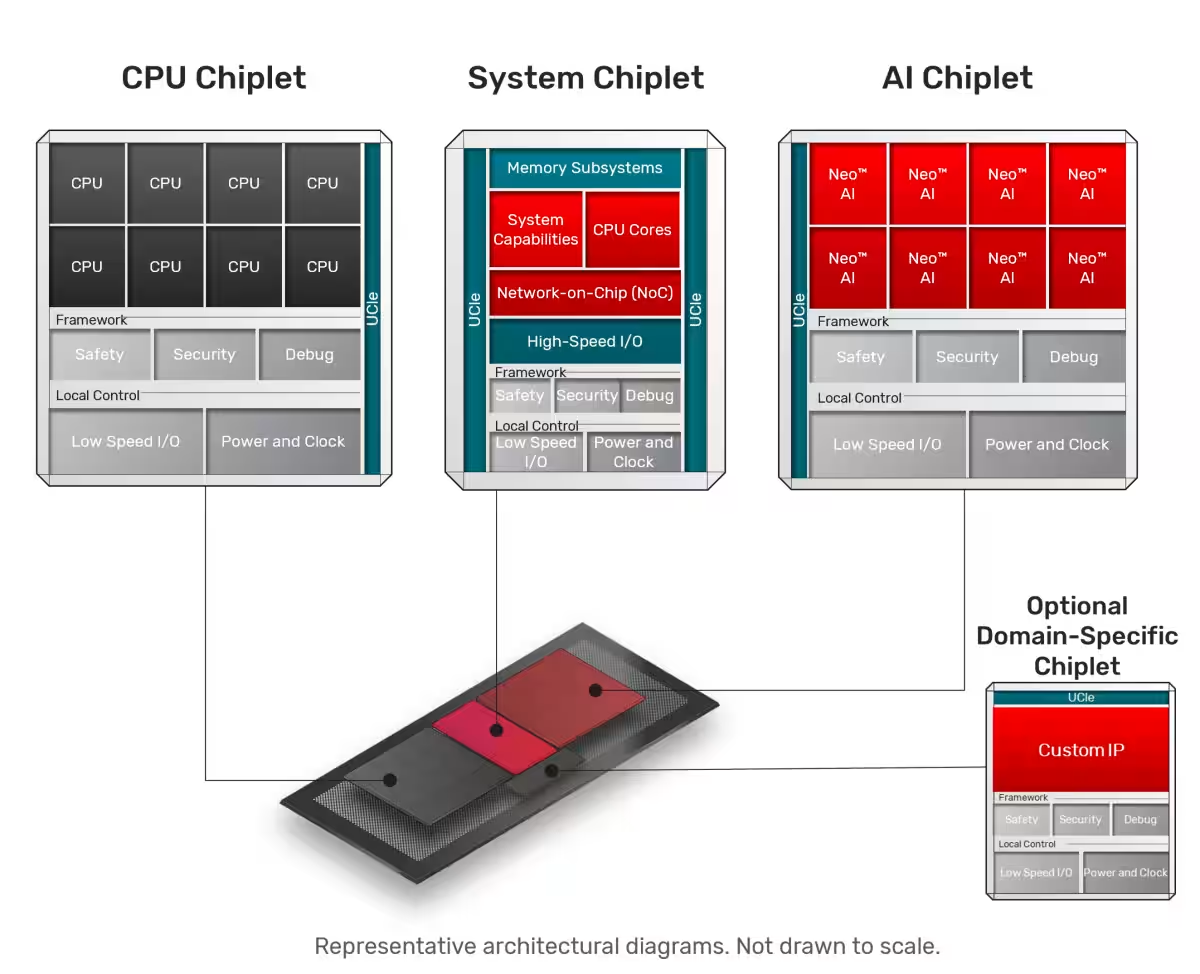

さらに、ケイデンスは自社及びサードパーティパートナーのIPにチップレット管理やセキュリティ、そして安全機能を組み合わせたチップレットフレームワークアーキテクチャを構築しています。これによる生成されたEDAフローは、Cadence Xcelium™ Logic Simulatorによるシミュレーション、さらにはCadence Palladium® Z3 Enterprise Emulation Platformでのエミュレーションとシームレスに連携し、物理設計フローにおいてもリアルタイムフィードバックによる効率的な配置配線プロセスを実現します。

デザインの基盤となるチップレットアーキテクチャは、Arm Chiplet System Architectureなどの業界標準に準拠しており、エコシステム内での相互運用性が強化されています。また、Universal Chiplet Interconnect Express™(UCIe™)IPにより、ダイ間の相互接続が可能となり、迅速なインターフェース統合が実現されます。

パートナー各社からの期待の声

各パートナー企業は、ケイデンスとの協力により生まれる新しいソリューションに期待を寄せています。例えば、Arm社のSuraj Gajendra氏は「このプラットフォームが次世代インテリジェントシステムの要件を満たし、デザインの複雑さを軽減することに貢献します」と述べています。Arteris社やeMemory社も、自社製品の強みをもってこのエコシステムをサポートしていく意向を示しています。

まとめ

ケイデンスの新たなチップレットエコシステムは、半導体業界において重要な意味を持つマイルストーンとなります。設計の複雑化が進む中で、より高い性能やコスト効率を実現するためにはマルチダイやチップレットベースのアーキテクチャは不可欠です。ケイデンスの整備するエコシステムを利用することで、様々な分野において新しいイノベーションを実現させる秘訣を見出すことができるでしょう。

トピックス(その他)

【記事の利用について】

タイトルと記事文章は、記事のあるページにリンクを張っていただければ、無料で利用できます。

※画像は、利用できませんのでご注意ください。

【リンクついて】

リンクフリーです。